湖南打線電子元器件鍍金廠家

電子元件鍍金工藝正經(jīng)歷著深刻變革,以契合不斷攀升的性能、環(huán)保及成本等多方面要求。性能層面,伴隨電子產(chǎn)品邁向高頻、高速、高集成化,對(duì)鍍金層性能提出了更高標(biāo)準(zhǔn)。在5G乃至未來6G無線通信領(lǐng)域,信號(hào)傳輸頻率飆升,電子元件鍍金層需憑借更低的表面電阻,全力降低高頻信號(hào)的趨膚效應(yīng)損耗,確保信號(hào)穩(wěn)定、高效傳輸,為超高速網(wǎng)絡(luò)連接筑牢根基。與此同時(shí),在極端環(huán)境應(yīng)用場(chǎng)景中,如航空航天、深海探測(cè)等,鍍金層不僅要扛住高低溫、強(qiáng)輻射、高鹽度等惡劣條件,保障電子元件正常運(yùn)行,還需進(jìn)一步提升自身的耐磨性、耐腐蝕性,延長(zhǎng)元件使用壽命。環(huán)保成為鍍金工藝發(fā)展的關(guān)鍵方向。傳統(tǒng)鍍金工藝大量使用含重金屬、**物等有害物質(zhì)的電鍍液,對(duì)環(huán)境危害極大。電子元器件鍍金,優(yōu)化表面硬度,減少磨損與接觸電阻。湖南打線電子元器件鍍金廠家

檢測(cè)鍍金層結(jié)合力的方法有多種,以下是一些常見的檢測(cè)方法:彎曲試驗(yàn)操作方法:將鍍金的電子元器件或樣品固定在彎曲試驗(yàn)機(jī)上,以一定的速度和角度進(jìn)行彎曲。通常彎曲角度在 90° 到 180° 之間,根據(jù)具體產(chǎn)品的要求而定。對(duì)于一些小型電子元器件,可能需要使用專門的微型彎曲夾具來進(jìn)行操作。結(jié)果判斷:觀察鍍金層在彎曲過程中及彎曲后是否出現(xiàn)起皮、剝落、裂紋等現(xiàn)象。如果鍍金層能夠承受規(guī)定的彎曲次數(shù)和角度而不出現(xiàn)明顯的結(jié)合力破壞跡象,則認(rèn)為結(jié)合力良好;反之,如果出現(xiàn)上述缺陷,則說明結(jié)合力不足。劃格試驗(yàn)操作方法:使用劃格器在鍍金層表面劃出一定尺寸和形狀的網(wǎng)格,網(wǎng)格的大小和間距通常根據(jù)鍍金層的厚度和產(chǎn)品要求來確定。一般來說,對(duì)于較薄的鍍金層,網(wǎng)格尺寸可以小一些,如 1mm×1mm;對(duì)于較厚的鍍金層,網(wǎng)格尺寸可適當(dāng)增大至 2mm×2mm 或 5mm×5mm。然后用膠帶粘貼在劃格區(qū)域,膠帶應(yīng)具有一定的粘性,能較好地粘附在鍍金層表面。粘貼后,迅速而均勻地將膠帶撕下。結(jié)果判斷:根據(jù)劃格區(qū)域內(nèi)鍍金層的脫落情況來評(píng)估結(jié)合力。按照相關(guān)標(biāo)準(zhǔn),如 ISO 2409 或 ASTM D3359 等標(biāo)準(zhǔn)進(jìn)行評(píng)級(jí)。陜西五金電子元器件鍍金鍍鎳線電子元器件鍍金,抗氧化強(qiáng),延長(zhǎng)元件使用壽命。

電子元件鍍金的重心優(yōu)勢(shì)1. 電氣性能優(yōu)異低接觸電阻:金的電阻率為 2.4μΩ?cm,遠(yuǎn)低于銅(1.7μΩ?cm)和銀(1.6μΩ?cm),且表面不易形成氧化層,可維持穩(wěn)定的導(dǎo)電性能。抗信號(hào)損耗:在高頻電路中,金鍍層可減少信號(hào)衰減,適合高速數(shù)據(jù)傳輸(如 HDMI 接口鍍金提升 4K 信號(hào)傳輸質(zhì)量)。2. 化學(xué)穩(wěn)定性強(qiáng)抗氧化與耐腐蝕:金在常溫下不與氧氣、水反應(yīng),也不易被酸(如鹽酸、硫酸)腐蝕,可在潮濕、鹽霧(如海洋環(huán)境)或工業(yè)廢氣環(huán)境中長(zhǎng)期使用(如海上風(fēng)電設(shè)備的電子元件)。抗硫化:避免與空氣中的硫(如 H?S)反應(yīng)生成硫化物(黑色膜層),而銀鍍層易硫化導(dǎo)致導(dǎo)電性能下降。3. 機(jī)械性能良好耐磨性:金鍍層(尤其是硬金)硬度可達(dá) 150~200HV,優(yōu)于純金(20~30HV),適合頻繁插拔的場(chǎng)景(如手機(jī)充電接口)。可焊性:金與焊料(如 Sn-Pb、無鉛焊料)結(jié)合力強(qiáng),焊接時(shí)不易產(chǎn)生虛焊(但需控制鍍層厚度,過厚可能導(dǎo)致焊點(diǎn)脆性增加)。4. 表面光潔度與可加工性鍍金層表面光滑,可減少灰塵、雜質(zhì)附著,同時(shí)適合精密加工(如蝕刻、電鍍圖形化),滿足微型化元件的需求(如 01005 尺寸的貼片電阻鍍金)。

鍍金工藝的關(guān)鍵參數(shù)與注意事項(xiàng)1. 鍍層厚度控制常規(guī)范圍:連接器、金手指:1~5μm(硬金,耐磨)。芯片鍵合、焊盤:0.1~1μm(軟金,可焊性好)。影響:厚度不足易導(dǎo)致磨損露底,過厚則增加成本且可能影響焊接(如金層過厚會(huì)與焊料形成脆性金屬間化合物 AuSn4)。2. 底層金屬選擇常見底層:鎳(Ni)、銅(Cu)。作用:鎳層可阻擋金與銅基板的擴(kuò)散(金銅互擴(kuò)散會(huì)導(dǎo)致接觸電阻升高),同時(shí)提供平整基底(如 ENIG 工藝中的鎳層厚度需≥5μm)。3. 環(huán)保與安全青化物問題:傳統(tǒng)電鍍金使用青化金鉀,需嚴(yán)格處理廢水(青化物劇毒),目前部分工藝已改用無氰鍍金(如亞硫酸鹽鍍金)。回收利用:鍍金廢料可通過電解或化學(xué)溶解回收金,降低成本并減少污染。4. 成本與性價(jià)比金價(jià)格較高(2025 年約 500 元 / 克),因此工藝設(shè)計(jì)需平衡性能與成本:高可靠性場(chǎng)景(俊工、航天):厚鍍金(5μm 以上)。消費(fèi)電子:薄鍍金(0.1~1μm)或局部鍍金。軍工級(jí)鍍金標(biāo)準(zhǔn),同遠(yuǎn)表面處理確保元器件長(zhǎng)效穩(wěn)定。

鍍金層的孔隙率過高會(huì)對(duì)電子元件產(chǎn)生諸多危害,具體如下:加速電化學(xué)腐蝕:孔隙會(huì)使底層金屬如鎳層暴露在空氣中,在潮濕或高溫環(huán)境中,暴露的鎳層容易與空氣中的氧氣或助焊劑中的化學(xué)物質(zhì)發(fā)生反應(yīng),形成氧化鎳或其他腐蝕產(chǎn)物,進(jìn)而加速電子元件的腐蝕,縮短其使用壽命。降低焊接可靠性:孔隙會(huì)導(dǎo)致焊接點(diǎn)的金屬間化合物不均勻分布,影響焊接強(qiáng)度和導(dǎo)電性能,使焊接點(diǎn)容易出現(xiàn)虛焊、脫焊等問題,降低電子元件焊接的可靠性,嚴(yán)重時(shí)會(huì)導(dǎo)致電路斷路,影響電子設(shè)備的正常運(yùn)行。增大接觸電阻:孔隙的存在可能使鍍金層表面不夠致密,影響電子元件的導(dǎo)電性,導(dǎo)致接觸電阻增大。這會(huì)增加信號(hào)傳輸過程中的能量損失,影響信號(hào)的穩(wěn)定性和清晰度,對(duì)于高頻信號(hào)傳輸?shù)碾娮釉赡軙?huì)造成信號(hào)衰減和失真。引發(fā)接觸故障:若基底金屬是銅,銅易向鍍金層擴(kuò)散,當(dāng)銅擴(kuò)散到表面后會(huì)在空氣中氧化生成氧化銅膜。同時(shí),孔隙會(huì)使鎳暴露在環(huán)境中,與大氣中的二氧化硫反應(yīng)生成硫酸鎳,該生成物絕緣且體積較大,會(huì)沿微孔蔓延至鍍金層上,導(dǎo)致接觸故障,影響電子元件的正常工作。鍍金工藝不達(dá)標(biāo)易導(dǎo)致鍍層脫落,影響元器件正常使用。江西高可靠電子元器件鍍金鈀

鍍金增強(qiáng)可焊性,讓焊接過程更順暢,焊點(diǎn)牢固可靠。湖南打線電子元器件鍍金廠家

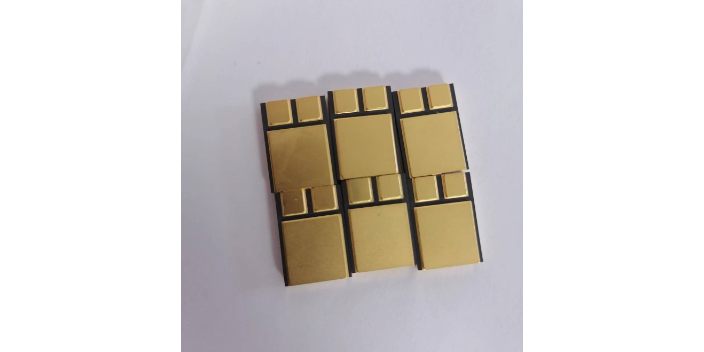

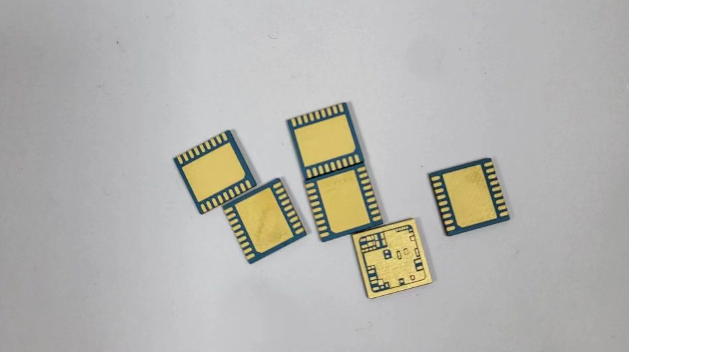

電子元器件鍍金工藝類型電子元器件鍍金工藝主要有電鍍金和化學(xué)鍍金。電鍍金是在直流電場(chǎng)作用下,使金離子在元器件表面還原沉積形成鍍層,通過控制電流密度、電鍍時(shí)間等參數(shù),可精確控制鍍層厚度與均勻性,適用于規(guī)則形狀、批量生產(chǎn)的元器件。化學(xué)鍍金則是利用氧化還原反應(yīng),在無外加電流的情況下,使溶液中的金離子在元器件表面自催化沉積,無需復(fù)雜的電鍍?cè)O(shè)備,能在形狀復(fù)雜、表面不規(guī)則的元器件上形成均勻鍍層,尤其適合對(duì)精度要求高、表面敏感的電子元器件。湖南打線電子元器件鍍金廠家

- 四川氧化鋁電子元器件鍍金供應(yīng)商 2025-07-26

- 廣東打線電子元器件鍍金鎳 2025-07-26

- 河北氧化鋁電子元器件鍍金鍍鎳線 2025-07-26

- 惠州金屬五金表面處理加工 2025-07-26

- 四川片式電子元器件鍍金電鍍線 2025-07-26

- 汕頭精密五金表面處理處理方式 2025-07-26

- 山東氮化鋁電子元器件鍍金車間 2025-07-26

- 北京五金電子元器件鍍金鍍鎳線 2025-07-26

- 重慶五金電子元器件鍍金鍍金線 2025-07-26

- 重慶芯片電子元器件鍍金電鍍線 2025-07-25

- 全拆分放大器介紹 2025-07-26

- 東莞氮化鎵材料刻蝕價(jià)錢 2025-07-26

- 光模塊通信模塊求購 2025-07-26

- 崇明區(qū)機(jī)電雙面膠帶 2025-07-26

- 山東按摩儀電源適配器代加工 2025-07-26

- 杭州醫(yī)療級(jí)FDA認(rèn)證加工件生產(chǎn) 2025-07-26

- 蘇州工字電感磁芯尺寸 2025-07-26

- 天津雙極型集成電路數(shù)字機(jī) 2025-07-26

- 廣州車輛控制單元VCU芯片潤(rùn)石芯片價(jià)格 2025-07-26

- 海南美信電源芯片 2025-07-26